港澳宝典资料大全港澳宝典资料大全实现突破平面光刻限制的超高密度均匀纳米线堆叠生长集成新技术

顺应摩尔定律的发展,大规模集成电路已经推进到N3-5纳米技术节点,而其中极深紫外光刻工艺却成为我国所面临的“掐脖子技术”之一。随着平面光刻工艺逐渐逼近物理极限,向垂直z方向要空间,采取更为先进的三维(3D)沟道结构已经成为国际公认的技术发展主流。近期Global Foundry,Samsung和Intel继推出了新一代全包裹栅(gate-all-around, GAA)纳米线沟道晶体管器件,其中最为关键的垂直堆叠纳米线沟道(vertically stacked discrete nanowire channels)需要首先进行多层SiGe/Si叠层外延生长,然后通过极深紫外光刻和选择性Ge层刻蚀等工艺实现。随着堆叠层数增加(以提供更大电流驱动),其制备成本将不断提高,并给保持分立沟道尺寸均匀性带来技术挑战。与“至上而下”的光刻技术相比,“至下而上”的纳米线沟道生长技术则更为高效、精细且富于变化。然而长期以来,由于难以实现精准的空间定位和均匀的尺寸调控,纳米线生长技术一直无法规模应用于器件集成。

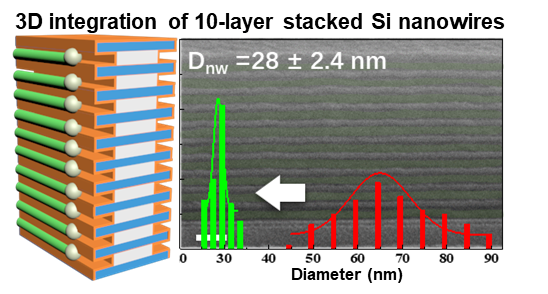

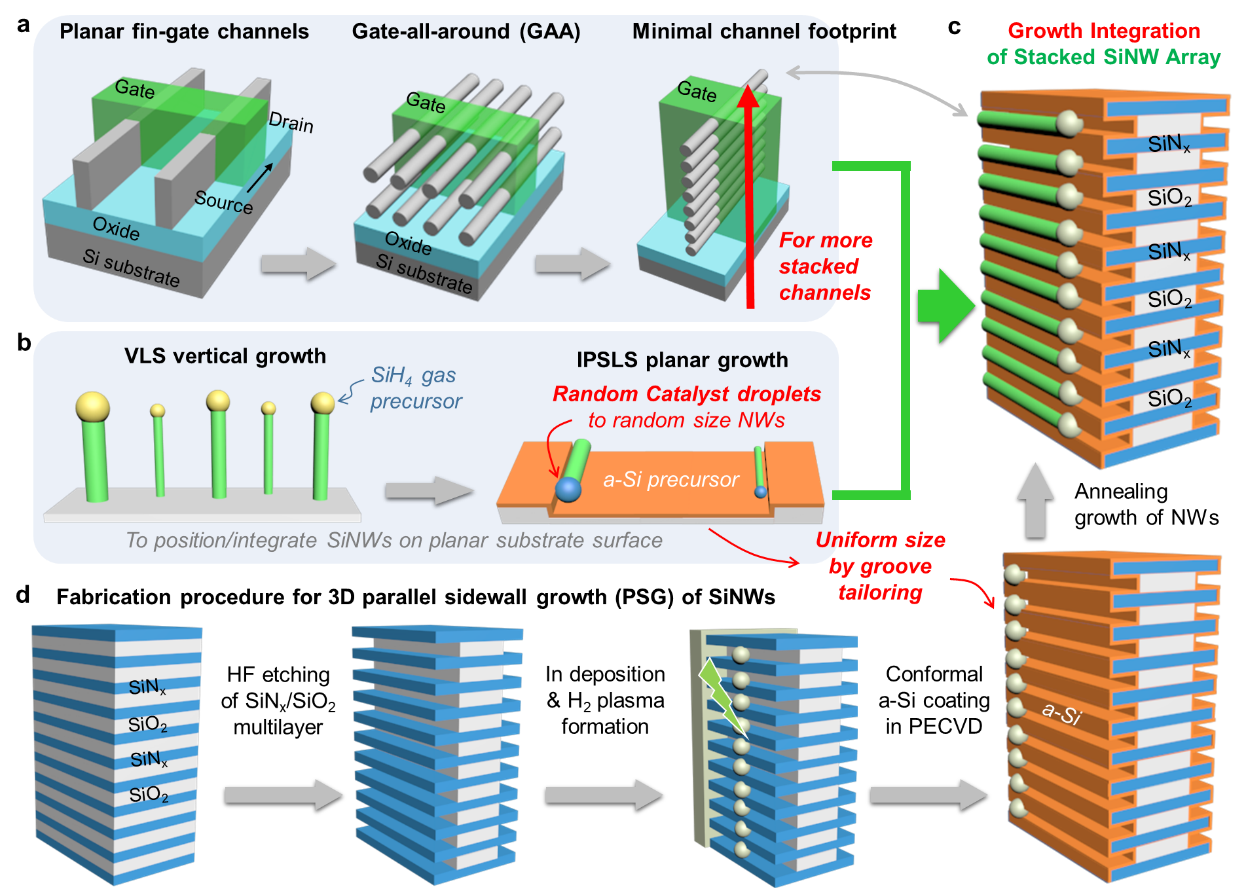

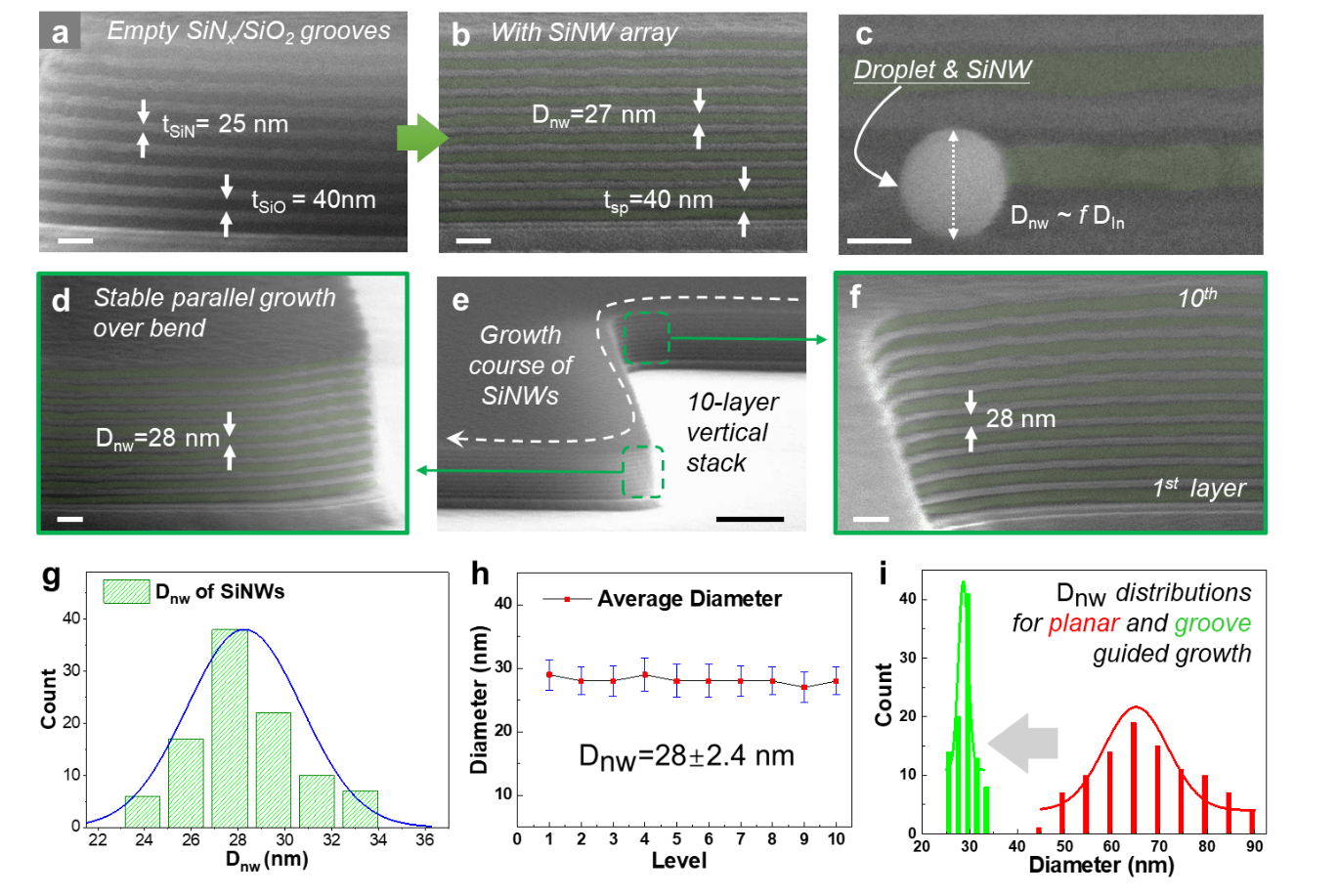

针对此技术挑战,港澳宝典资料大全港澳宝典资料大全余林蔚教授和王军转副教授提出利用团队基础原创的平面IPSLS纳米线生长模式,在非晶氮化硅(SiN)/氧化硅(SiO)叠层刻蚀侧壁上,通过选择性刻蚀形成高密度引导台阶,平行生长制备出尺寸均匀()的超高密度(间隔<40 nm)晶硅纳米线阵列。研究发现,高密度侧壁沟槽对催化铟颗粒的形成具有显著的调制作用,在氮氧叠层侧壁上形成小于铟原子表面扩散长度的沟槽结构是控制纳米线沟道均匀性的关键,同时突出的氮层宽度对调控相邻生长纳米线结构之间的耦合竞争有重要影响。值得一提的是,通过此低温侧壁平行生长可以大规模制备多达10层的堆叠纳米线沟道结构,其中纳米线的直径、界面形貌和间隔密度可通过氮氧叠层的淀积厚度和刻蚀时间精确调控,从而避免了对高成本Si/GeSi多层叠层外延和极深紫外光刻技术的依赖。通过此技术可以大幅压缩FET器件的沟道投影面积,有望应用于利用较低光刻节点技术(例如N65~90纳米)实现等效于N5节点技术的更高器件集成密度。此项研究建立在课题组近期在3D纳米线生长调控的基础之上(见后续列表),首次展示了精控纳米生长技术在高均匀性尺寸调控和大规模三维构架制备上的巨大潜力,其低温生长技术(<350 oC)也为实现真正意义上的Monolithic 3D前端-后端器件集成带来了全新的技术可能和突破方向。

图1:非晶氮化硅(SiN)/氧化硅(SiO)超晶格侧壁调制生长超高密度均匀堆叠硅纳米线阵列结构。

图2:堆叠纳米线生长制备基本流程,以及与传统FET器件结构和生长模式的比较。

图3:堆叠纳米线生长结构表征和尺寸调控统计分析。

工作近期发表于美国化学学会《纳米快报》上:Unprecedented Uniform 3D Growth Integration of 10-Layer Stacked Si Nanowires on Tightly Confined Sidewall Grooves, Nano Letters 20 (10), 10.1021/acs.nanolett.0c02950 (2020)。其中,博士生胡瑞金同学为第一作者,王军转副教授和余林蔚教授为共同通讯作者,研究工作得到了港澳宝典资料大全徐骏教授、施毅教授和陈坤基教授的悉心指导和大力支持。相关技术成果已经通过与华为公司合作共同提交申请了多项技术专利。该项研究工作受到海外高层次人才青年计划,国家自然科学基金,江苏省杰出青年基金和双创人才计划资助。

论文链接: https://pubs.acs.org/doi/10.1021/acs.nanolett.0c02950

附件:课题组3D生长调控的相关前期工作:

Cylindrical Line-Feeding Growth of Free-Standing Silicon Nanohelices as Elastic Springs and Resonators

Haiguang Ma, Rongrong Yuan, Junzhuan Wang, Yi Shi, Jun Xu, Kunji Chen, and Linwei Yu*

Nano Letters20, 5072–5080 (2020) Cover Report

https://pubs.acs.org/doi/full/10.1021/acs.nanolett.0c01265?ref=recommended

Facile 3D integration of Si nanowires on Bosch-etched sidewalls for stacked channel transistors

Ruijin Hu, Haiguang Ma, Han Yin, Jun Xu, Kun Ji Chen and Linwei Yu*

Nanoscale 12, 2787-2792 (2020)

https://pubs.rsc.org/en/Content/ArticleLanding/NR/2020/C9NR09000B#!divAbstract3D sidewall integration of ultra-high density silicon nanowires for stacked channel electronics

Xiaoxiang Wu, Haiguang Ma, Han Yin, Danfeng Pan, Junzhuan Wang, Linwei Yu,* Jun Xu, Yi Shi, Kunji Chen

Advanced Electronic Materials 5, 1800627 (2019)

https://www.onlinelibrary.wiley.com/doi/10.1002/aelm.201800627Planar Growth, Integration and Applications of Semiconducting Nanowires

Ying Sun, Taige Dong, Linwei Yu*, Jun Xu* and Kunji Chen

Advanced Materials31, 1903945 (2019)

https://onlinelibrary.wiley.com/doi/abs/10.1002/adma.201903945Monolithic integration of silicon nanowire networks as a soft wafer for highly stretchable and transparent electronics

Taige Dong, Ying Sun, Zhimin Zhu, Xiaoxiang Wu, Junzhuan Wang, Yi Shi, Jun Xu, Kunji Chen and Linwei Yu*

Nano Letters 19, 6235-6243 (2019)

https://pubs.acs.org/doi/10.1021/acs.nanolett.9b02291

课题组欢迎有志于三维电子集成应用的有志青年报考博士、博士后及专职科研岗职位!

联系人:余林蔚,[email protected]